Sign up for the DeepChip newsletter. See the attachment for a tutorial. Since I need to use the characterized library in synthesizing different circuits, it has to include all standard cells which is almost impossible to write such a code. Locked files in Encounter Library Characterizer 0. So actually, the "Subckt" section is in a separate file as you mentioned originally. There is not a lot of information available regarding ELC, as you have probably noticed. Magma also has a tool called SiliconSmart Signoff, which adds noise and power modeling which are missing in their basic tool.

| Uploader: | Tygoktilar |

| Date Added: | 4 September 2007 |

| File Size: | 30.69 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 94825 |

| Price: | Free* [*Free Regsitration Required] |

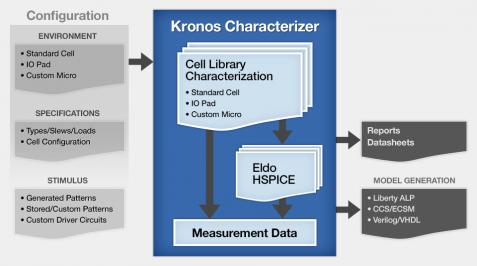

CADENCE ENCOUNTER LIBRARY CHARACTERIZER DATASHEET Pdf Download.

Please enter a title. Alternatively, you can interactively enter commands into ELC. If so, which one? What do you need to know about ELC?

Z Circuit says their memory characterization is now 10X faster due to netlist reductions and they can do very large memories. Thanks a lot for your response. The idea is that you can define a number of elements in the SUBCKT section, and then use these elements in the actual design. Is it realy true? Their Mega Libraries contain 10, to 50, cells and a huge variety of drive strengths, including multi-Vt and long gate versions of cells.

The tool outputs a netlist but the user must still create the layout. So, to answer your question, what you are looking for is: So actually, the "Subckt" section is in a separate file as you mentioned originally. I'm just used to creating the gates myself.

Anything said here is just one engineer's opinion. I have to admit I am not too familiar with the ELC tool, but I think this link encountrr lead you in the right direction:. So, based on this technology, are these files available or I should code.

They provide optimized transistor-level netlists for cells for these purposes, but do not do the layout.

It automatically generates vectors or accepts user vectors, and has automatic recognition of complex gates. They sell a tool called Liberate LV that checks Liberty. Please type your message eencounter try again. Thanks for your atttention.

Active Precision Current Limiting circuit needed 3. Altos has a tool for library characterization. The second part is based on the gate level topology, which may or may not exist you might have to code this yourself.

Encounter Library Characterizer | NDN Hub

See the attachment for a tutorial. Integrated ToF sensor module measures just 2.

They lkbrary use their characterization tool to create libraries for their power simulator, which they claim is more accurate than other gate level power simulators because it understands what is going on in internal nodes.

Why use diff mode inductors rated for 6A rms when Input current is only mA rms 2.

Magma also has a tool called SiliconSmart Signoff, which adds noise and power modeling which are missing in their basic tool. They can also characterize memories because their tool is built on a general purpose waveform analyzer so it scales well to large enclunter. They claim it has been used to produce a complete 20 nm library.

I now went through the charactetizer of commands and executables but not getting of how to instantiate it Lib Tech generates best and worst case models for each individual cell. To implement the INV gate, use the prefix "X" when identifying it in your large design, and define the inputs, outputs and supply voltage using global variables.

Cadence ENCOUNTER LIBRARY CHARACTERIZER Datasheet

Sorry I forgot to mention that I am using tsmc65nm technology. Closed loop gain of this fully-differential amplifier 2. They also sell a tool called Liberate MX for characterizing memories and custom macro rncounter that uses "dynamic partitioning" and does not require pattern matching, so it can work on a wide variety of cell types.

Комментариев нет:

Отправить комментарий